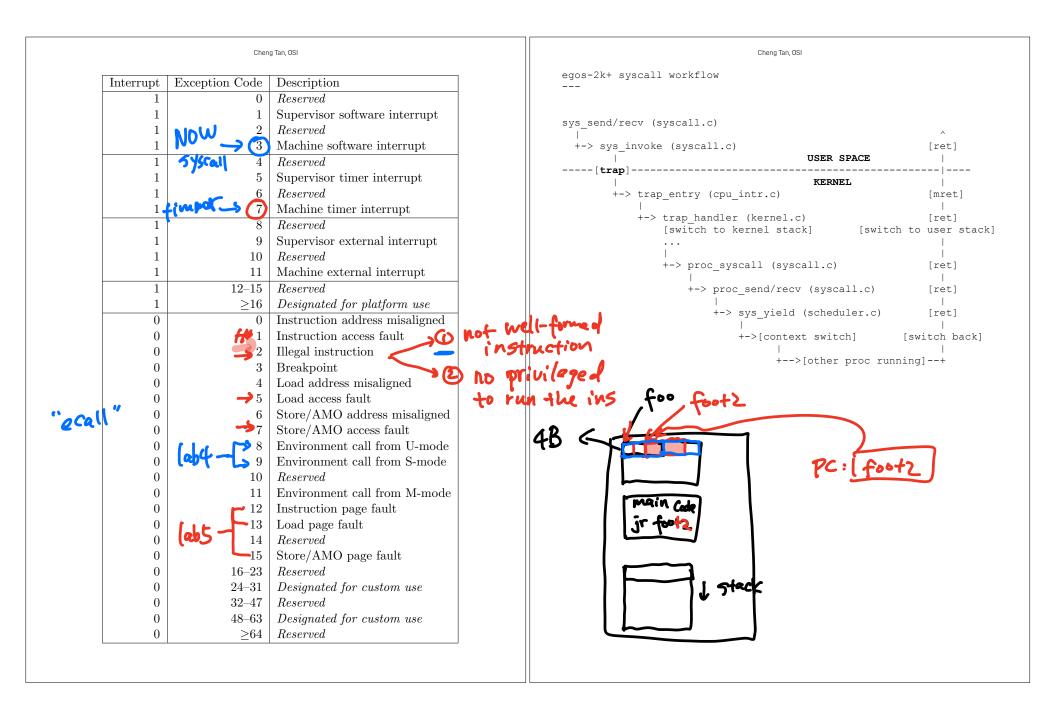

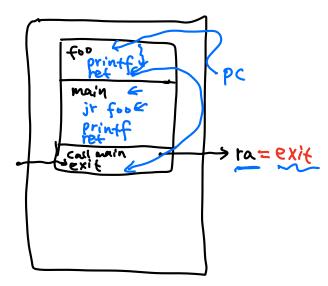

Week 6 CS4973/CS6640 02/10 2025 RISC-U https://naizhengtan.github.io/25spring/ most last time: egos earth: N  $\rightarrow$  diff: 🗹 2. egos exception handling ☑ 3. syscall in egos () instruction Grass. □ 4. CPU privilege levels registers □ 5. System virtualization AIS PICS · Lab4 : OS protection other monolithic-Kernel, micro-kernel 1. last time: egos \\*/OS organization 🗸 egos design Sys\_file 645-proc ✓ egos boot proc tur calls fs \* kernel ~= three handlers prous Kernel grass boot: earth CPU 0x2040\_000 L> earth.S HW Ly main (earth.c) ways to trap L's main cgrass.c) to kernel? L> sys\_proc Gyszfile Gyszdir ⇒ syszshell · interrupt · Syscall 5\$ ~ 7 · exception

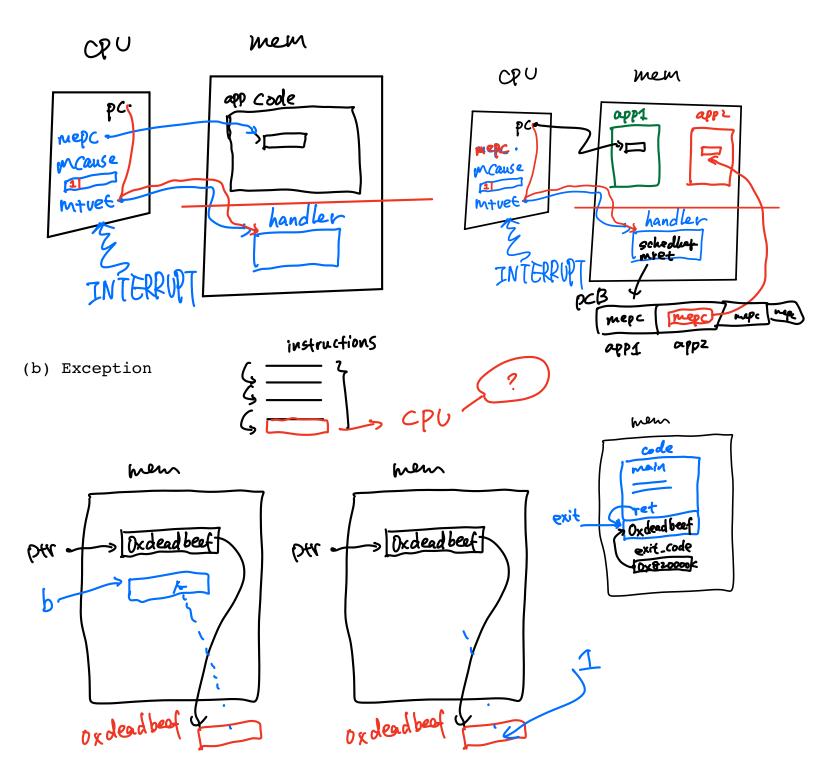

(a) Interrupt

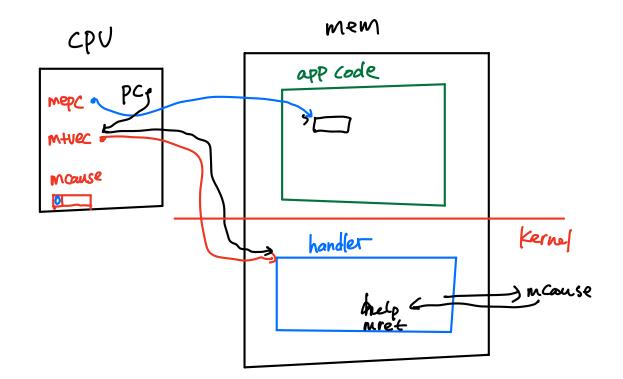

triggered?

Mivec

Q: After handling an interrupt, where does the CPU resume execution?

Q: How does the CPU determine what to execute when an interrupt is

> what code

CSR

mref

mepc

Q: How does the kernel identify which interrupt was triggered?

## MCause

C. Linux.

##

LSKipped

Q: How could I know what privilege level the current CPU is running in?

## ....

RISC-V deliberately doesn't make it easy for code to discover what mode it is running it because this is a virtualisation hole. As a general principle, code should be designed for and implicitly know what mode it will run in. Applications code should assume it is in U mode. The operating system should assume it is in S mode (it might in fact be virtualised and running in U mode, with things U mode can't do trapped and emulated by the hypervisor).

[from https://forums.sifive.com/t/how-to-determine-the-current-executionprivilege-mode/2823]